Quartus2 V13.1 ~Tips編 VHDL記述による合成結果の違い~

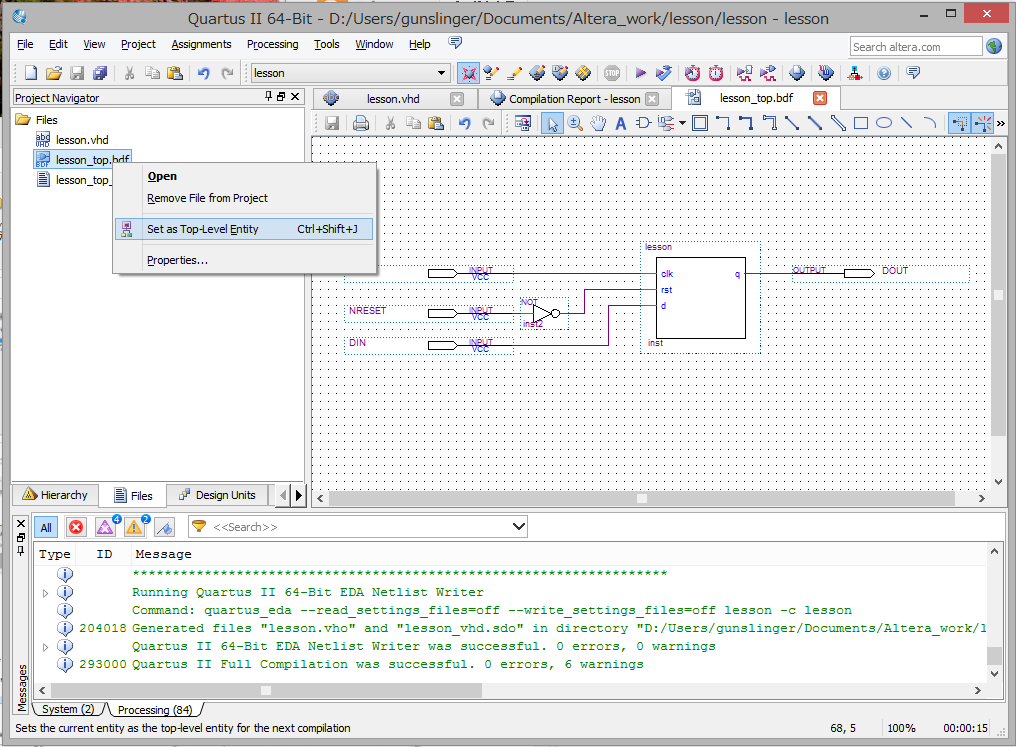

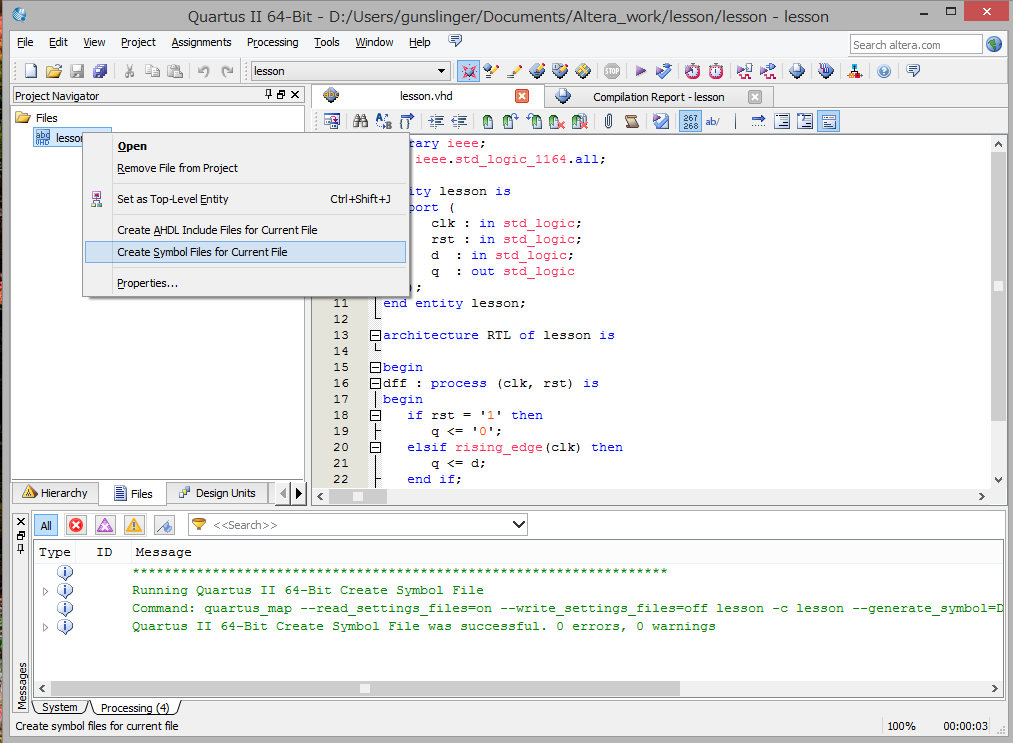

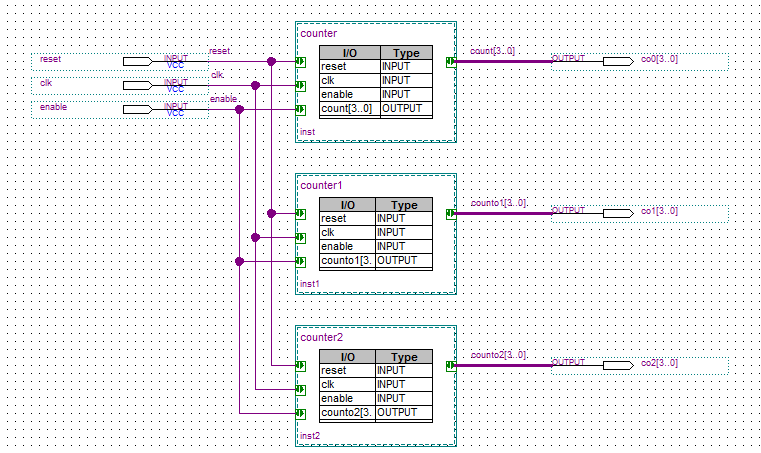

HDL記述は、高級言語でのプログラム記述と同様に、コンパイラの癖や性能によって、合成結果(回路、規模など)が大きく異なる場合があります。 デジタル設計での必須アイテムであるカウンタの記述にて、Quartus2の合成結果を見比べてみました。 ■仕様 4bitの13進同期式カウンタ 非同期リセット入力有り カウントイネーブル入力有り ■トップ回路図 ■COUNTERのVHDL記述 カウンターの出力変数をintegerで定義しています。桁数が大きい時やシーケンサなどを記述する時には読みやすいので使いやすいですね。 ARCHITECTURE counter_architecture OF counter IS signal counto : integer; BEGIN count <= CONV_STD_LOGIC_VECTOR(counto,4); process (clk, reset, enable) begin if (reset = '1') then counto <= 0; elsif (rising_edge(clk)) then if (enable = '1') then if(counto = 12) then counto <= 0; else counto <= counto + 1; end if; end if; end if; end process; END counter_architecture; ■COUNTER1のVHDL記述 integerを使用せず、std_logic_vectorで記述したものです。ビット幅が大きくなると間違い易い記述です。 ARCHITECTURE counter1_architecture OF counter1 IS signal counto : STD_LOGIC_VECTOR(3 downto 0); BEGIN counto1 <= counto; process (clk, res